# GLOBAL JOURNAL OF ENGINEERING SCIENCE AND RESEARCHES REVIEW ON TWO LEGGED THREE PHASE THREE LEVEL INVERTER USING SVPWM

# Jinsha K V<sup>\*1</sup> & Kiran T S<sup>2</sup>

<sup>\*1</sup>M Tech scholar, Department of ECE, College Of Engineering Thalassery, Kerala, India <sup>2</sup>Assistant Professor, Department of ECE, College Of Engineering Thalassery, Kerala, India

# ABSTRACT

Multilevel inverter technology finds significant applications in the area of high-power medium-voltage energy control Multilevel inverters generate sinusoidal voltages from discrete voltage levels, and pulse width-modulation (PWM) strategies accomplish this task of generating sinusoids of variable voltage and frequencies.. The two main techniques of PWM generation for multilevel inverters are sine-triangle PWM (SPWM) and space vector PWM (SVPWM). Multilevel SPWM involves the comparison of a reference signal with a number of level shifted carriers to generate the PWM signal. SVPWM involves synthesizing the reference voltage space vector by switching among the three nearest voltage space vectors. A conventional method of SVPWM generation for three legged three phase two level inverter and a modified method also discussed.

**Keywords-** two legged multilevel inverters, Space vector pulse width modulation [SVPWM], Four switch three phase inverter (FSTPI).

# I. INTRODUCTION

Multilevel Inverter Technology has emerged as a powerful technique in the area of medium voltage high power applications. Multilevel inverter synthesizes desired output voltage from multiple levels of dc voltages. As the number of voltage level increases the harmonic content of output voltage waveform decreases significantly. Multilevel inverters gained more attention in recent years due to its inherent advantages of high Voltage-Ampere rating and good harmonic rejection capabilities. The requirement of more number of semiconductor switches is the major disadvantage of multilevel inverters. Although low voltage rated switches can be used in a multilevel inverter, each switch requires a related gate drive protection circuits. Hence the overall system becomes more complex and expensive. In addition increased number of switches increases the switching losses and electromagnetic interference (EMI). So in many practical applications for efficient operation of multilevel inverters, reduction in the number of power semiconductor switches for the inverters is drawing significant research attention. The four-switch threephase inverter [FSTPI] topology is one of the techniques to reduce the switches in the inverter. In comparison with the usual three-phase voltage-source inverter with six switches, four-switch three-phase inverter uses only two legs, with a pair of complementary power switches in each leg. Reduction in the number of power switches, switching driver circuits, conduction losses and total price are the main features of FSTPI topology. For efficient operation of multilevel inverters various pulse width modulation (PWM) techniques are used. The most popular PWM techniques used in multilevel inverters are Sine-Triangle PWM (SPWM) and space vector PWM (SVPWM). In multilevel SPWM, PWM signal is generated by comparing sine wave with a number of levels shifted triangular carrier signals. If an 'n level' inverter is used, 'n-1 carriers' will be needed. With the developments of digital signal processors SVPWM technique become most popular PWM method and it utilizes the space vector concept for computing the duty cycle of the switches. In SVPWM scheme, the reference voltage space vector is synthesized by switching the three nearest voltage space vectors among the inverter voltage vectors.

# II. GENERAL PWM STRATEGY FOR FOUR-SWITCH THREE-PHASE INVERTERS

A general pulse width modulation (PWM) method for control of four-switch three-phase inverters is presented. The proposed vector PWM offers a simple method to select three or four vectors that effectively synthesize the desired output voltage, even in presence of voltage oscillations across the two dc-link capacitors. The method utilizes the so

called space vector modulation, and includes its scalar version. Different vector combinations are compared. The effect of Wye and delta motor winding connections over the pulse width modulator is also considered. The common mode voltage generated by the four-switch three-phase converter is evaluated and compared to that provided by the standard six-switch three-phase inverter. Simulation and experimental results are presented to demonstrate the feasibility of the proposed approach.

### A. Proposed Method

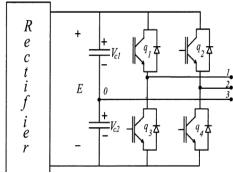

The proposed vector PWM offers a simple method to select three or four vectors that effectively synthesize the desired output voltage, even in presence of voltage oscillations across the two dc-link capacitors. The method utilizes the so called space vector modulation, and includes its scalar version. Different vector combinations are compared. The common mode voltage generated by the four-switch three-phase converter is evaluated and compared to that provided by the standard six-switch three-phase inverter. Simulation and experimental results are presented to demonstrate the feasibility of the proposed approach. A standard three-phase voltage source inverter utilizes three legs [six-switch three-phase voltage source inverter(SSTPI)], with a pair of complementary power switches per phase. A reduced switch count voltage source inverter [four switch three-phase voltage source inverter (FSTPI)] uses only two legs, with four switches, as shown in Fig. 1(a). The proposed method provides a simple way to select either three, or four vectors to synthesize the desired output voltage during the switching period. In the proposed approach, the selection between three or four vectors is parameterized by a single variable. This permits to implement all alternatives, thus allowing for a fair comparison of the different modulation techniques.

Fig. 1. AC drive system configuration.

#### **B.** Space Vector Analysis

With respect to the circuit shown in Fig. 1(a) it is assumed that the conduction state of the power switches is associated with binary variables q1 to q4. Therefore, a binary "1" will indicate a closed switch, while "0" will indicate the open state. Pairs q1-q3andq2-q4 are complementary and, as a consequence, q3=1-q1and q2=1-q4. Also it will be assumed that a stiff voltage is available across the two dc-link capacitors, and2, where corresponds to a stiff dc-link voltage, i.e., the actual value of the dc-link voltage is equal to E.

TABLE ~ I Available Vectors in the  $\alpha\beta$  Plane for the Wye Connection

| $q_1$ | $q_2$ | $\mathbf{v} = v_{\alpha} + j v_{\beta}$         |

|-------|-------|-------------------------------------------------|

| 0     | 0     | $\mathbf{v}_1 = (\bar{E}/\sqrt{6})e^{-j2\pi/3}$ |

| 1     | 0     | $\mathbf{v}_2 = (\bar{E}/\sqrt{2})e^{-j\pi/6}$  |

| 1     | 1     | $\mathbf{v}_3 = (\bar{E}/\sqrt{6})e^{j\pi/3}$   |

| 0     | 1     | $\mathbf{v}_4 = (\bar{E}/\sqrt{2})e^{j5\pi/6}$  |

(C)Global Journal Of Engineering Science And Researches

Pole voltages v10,v20 v30 and depend on the states of the power switches. They can be expressed in terms of the binary variables q1 and q2, and the dc-link voltage as follows:

$$v_{10} = (2q_1 - 1)\frac{\bar{E}}{\frac{2}{\bar{E}}} \tag{1}$$

$$v_{20} = (2q_2 - 1)\frac{L}{2}$$

(2)

$$v_{20} = 0$$

(3)

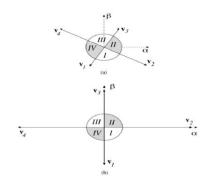

Fig. 2. Vectors in the  $\alpha\beta$  plane for the same dc bus voltage: (a)Wye connection and (b) delta connection.

Space vector modulation, and the problem of selecting the appropriate switching sequence are better understood, if the three phase quantities are transformed into  $\alpha \beta$  quantities. The transformed  $\alpha \beta$  variables are given by  $v_{\alpha\beta}$

$$v_{\alpha\beta} = A v_{123} \tag{4}$$

with, and the transformation  $v_{123} = [v1 \ v2 \ v3]^T v_{\alpha\beta} = [v_{\alpha} v_{\beta}]^T$  matrix being read as

$$A = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -1/2 & -1/2 \\ 0 & \sqrt{3}/2 & -\sqrt{3}/2 \end{bmatrix}.$$

(5)

# III. FRACTAL BASED SPACE VECTOR PWM FOR MULTILEVEL INVERTERS—A NOVEL APPROACH

A space vector pulse width-modulation (SVPWM) technique based on fractal approach for multilevel inverters is presented. This paper proposes a view that the space vector locations of multilevel inverters possess a fractal structure, and the properties of fractal structure together with the simplicity of fractal arithmetic are exploited to generate the SVPWM. The proposed method does not use any lookup tables for sector identification. The switching space vectors are also directly determined without using any lookup tables. The proposed scheme can be extended to an *n*-level inverter, and a generalized algorithm is also presented. The proposed scheme for generating SVPWM for multilevel inverters is explained for a five-level inverter, and experimental results are presented for a three-level inverter.

#### A. Proposed Method

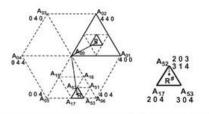

This section explains the proposed method for the generation of SVPWM for a five-level inverter, using the inherent fractal structure associated with the switching voltage space vector representation of multilevel inverter. The implementation of SVPWM involves the following four stages: 1) sector identification;2) determination of

switching voltage space vectors; 3) determination of the duration of each of the determined switching voltage space vectors; and 4) determination of an optimum switching sequence.

#### B. Sector Identification and Switching Vector Determination

Sector identification determines the triangle that encloses the tip of the reference space vector. In the proposed method, sector identification is done using the principle of repeated triangularization. The vertices of triangle (sector) represent the locations of switching voltage space vectors used to synthesize the reference space vector. From the instantaneous values of the three reference phase voltages Va, Vb, and Vc, the ( $\alpha$ ,  $\beta$ ) coordinates of the voltage space vector are determined. For a five-level inverter, the switching vectors located at the six vertices of the hexagon forming the periphery are the same as the vectors of equivalent two-level inverter, having the switching states as 4 0 0, 4 4 0, 0 4 0, 0 4 4, 0 0 4, and 4 0 4. A reference space vector A00P is considered for explaining the proposed method of sector identification for a five-level inverter (Figs. 4 and 5). The proposed method of sector identification begins with determining the location of the tip of the reference space vectorA00P from among the six regions of the equivalent two-level inverter. The step is implemented by comparison of instantaneous reference phase voltages [12], [14]. In this case, the reference space vectorA00P is located in region I of equivalent two-level inverter. The region I, from Fig. 1(a), is formed by the vertices A00, A01, and A02. The coordinates of the vertices are (0, 0), (4, 0), and  $(2, 2\sqrt{3})$ , respectively, as shown in Fig. 5(a). The switching states corresponding to the vectors located at A00, A01, and A02 are also shown in Fig. 5(a). For a five-level inverter, the total number of iterations of the triangularization algorithm is two. In the first application of the triangularization algorithm to the region enclosing the reference space vector(region I of equivalent two-level inverter), it gets divided into four smaller triangular regions. Equations (1)-(3) will generate the coordinates of the new voltage space vectors located at A11,A12, and A13, and simultaneously, (4)–(6) generate the inverter states corresponding to these new switching vectors. The three new voltage space vectors divide region I into four smaller triangular regions marked R1, R2, R3, and R4 in Fig. 5(b). The coordinates of the centroid of an equilateral triangle can be determined as the average of coordinates of the three vertices. For an equilateral triangle with the coordinates of the vertices as  $(\alpha 1, \beta 1), (\alpha 2, \beta 2), (\alpha 2, \beta 2$ and  $(\alpha 3, \beta 3)$ , the coordinates of the centroid ( $\alpha$ cent,  $\beta$ cent) are given by

$$\alpha_{\text{cent}} = \frac{1}{3}(\alpha_1 + \alpha_2 + \alpha_3)$$

$$\beta_{\text{cent}} = \frac{1}{3}(\beta_1 + \beta_2 + \beta_3).$$

The triangle with centroid closest to tip of reference space vector is  $\Delta$ A11A12A13.As pointed out earlier, for a fivelevel inverter, the *triangularization algorithm* has to be applied once more. The application of (1)–(6) to  $\Delta$ A11A12A13 will further generate three new voltage space vectors and, also, the inverter states corresponding to these new voltage vectors, thus dividing it into four smaller triangles[Fig. 5(c)]. From among these four triangles, the triangle enclosing the reference space vectorA00P is  $\Delta$ A23A25A26, as its centroid is closest to tip of the reference space vector. The sector is identified, and the inverter states corresponding to the switching vectors located at the vertices of the identified sector are also generated simultaneously

#### C. Switching Vector Time Calculation

The next stage in the generation of SVPWM through the proposed method involves determining the duration for which the voltage space vectors located at the vertices of the identified sector are to be switched. The determination of the duration of operation of the switching voltage space vectors is simplified by mapping the sector that is identified to enclose the reference space vector to sector of a two-level inverter [14], [15]. The mapping of the identified sector to a sector of the two-level inverter is done by mapping one of the three vectors of the identified sector to the actual zero vector in the voltage space vector representation of the inverter. In this paper, the vector selected to be mapped to the actual zero vector is referred as *virtual zero vector*. The vector with minimum value for the sum of magnitudes of  $\alpha$  and  $\beta$  coordinates is chosen to be the *virtual zero vector* for a particular sector. Therefore, the chosen *virtual zero vector* is the vector at minimum offset from zero vector. As determined in sector identification, the reference voltage space vectorA00P lies in the sector formed by the voltage space vectors located at A23, A25,

and A26. From Fig. 5(c), the coordinates of the space vectors located at A23, A25, and A26are  $(1,\sqrt{3}/2)$ ,  $(3,\sqrt{3}/2)$ , and  $(2,\sqrt{3})$ , respectively. The voltage space vector located at A23 is chosen as the virtual zero vector, and the sector enclosing the reference space vectorA00P gets mapped to region I of the two-level inverter. After mapping, using the conventional equations in Table I, the duration of the nonzero switching voltage space vectors (T1 and T2) is determined. The duration of the third vector (T0), which is the virtual zero vector, is also determined. From the determined T0, T1,and T2, the actual inverter leg switching times, designated as Tga, Tgb, and Tgc, are also determined as in [12]. The Tga,Tgb, and Tgc signals are used to generate the three PWM signals PWM\_A, PWM\_B, and PWM\_C, respectively.

| TABLE 11                                                     |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| EQUATIONS FOR DETERMINING T1 AND T2 FOR A TWO-LEVEL INVERTER |  |  |  |  |  |  |  |  |  |

| Sector | T <sub>1</sub>                                               | T <sub>2</sub>                                                |  |

|--------|--------------------------------------------------------------|---------------------------------------------------------------|--|

| Ι      | $T_{s}\left[V_{\alpha} - \frac{V_{\beta}}{\sqrt{3}}\right]$  | $T_8 \left[ \frac{V \beta}{0.866} \right]$                    |  |

| п      | $T_{s}\left[V_{\alpha} + \frac{V_{\beta}}{\sqrt{3}}\right]$  | $T_{s}\left[-V_{\alpha} + \frac{V_{\beta}}{\sqrt{3}}\right]$  |  |

| ш      | $T_{S}\left[\frac{V \beta}{0.866}\right]$                    | $-T_8 \left[ V_{\alpha} + \frac{V_{\beta}}{\sqrt{3}} \right]$ |  |

| IV     | $T_{S}\left[-V_{\alpha} + \frac{V_{\beta}}{\sqrt{3}}\right]$ | $-T_{8}\left[\frac{V \beta}{0.866}\right]$                    |  |

| v      | $-T_{S}\left[V_{\alpha} + \frac{V_{\beta}}{\sqrt{3}}\right]$ | $T_{s}\left[V_{\alpha} - \frac{V_{\beta}}{\sqrt{3}}\right]$   |  |

| VI     | $-T_{s}\left[\frac{V\beta}{0.866}\right]$                    | $T_s \left[ V_{\alpha} + \frac{V_{\beta}}{\sqrt{3}} \right]$  |  |

#### D. Optimized Switching Sequence Selection

Once the switching vectors are determined and their respective durations are calculated, then vectors are to be switched in an optimum sequence such that only one switching occurs when the inverter changes its state. In the space phasor PWM technique, the optimum switching is achieved by using the redundant states of the zero vector for alternate switching cycles. In this paper, the optimum switching is achieved by using two redundant switching states of the respective virtual zero vector in the alternate cycles. For every sector, the switching of the voltage space vectors starts and ends at the redundant states of the virtual zero vector. This is explained for the sector corresponding to the location of the reference space vectorA00P, as in Fig. 5. As already determined, the tip of the reference vector A00P is located in the sector formed by the vectors located at A23, A25, and A26 of which A23 is chosen as the virtual zero vector. The switching states corresponding to these switching vectors with redundancies are A23 (2 1 0,3 2 1, 4 3 2), A25 (3 1 0, 4 2 1), and A26 (3 2 0, 4 3 1). The virtual zero vector at A23 has three redundant switching states, while the voltage vectors at A25 and A26 have two redundant states each. In this paper, the redundancy is resolved by adopting a strategy that, if the redundancy of the virtual zero vector is greater than two, any of the redundant states of the virtual zero vector other than the last redundant state is selected. It can be verified that, if the last redundant state is chosen, the resulting sequence which starts and ends with the virtual zero vector will not result in an optimum sequence. The selected redundant state of the virtual zero vector is first switched in a particular sampling interval. The switching states of the other vectors are automatically generated using the selected redundant state of the virtual zero vector and the PWM signals. The sector formed by the vectors located at A23, A25, and A26, with the voltage space vector located at A23 selected as the virtual zero vector, is mapped to sector I of the two-level inverter. When the PWM signals for the three phases are generated using Tga, Tgb, and Tgc for sector I, the switching occurs first in phase A followed by phases B and C, which implies that Tga>Tgb>Tgc. For the sector formed by the voltage space vectors located at A23,A25, and A26, the redundant switching state of the virtual zero vector selected is (3 2 1). When the PWM A goes high,

fig 3 Mapping of a reference space vector  $\overline{\Lambda_{00}R}$  by choosing the vector located at  $\Lambda_{52}$  as the virtual zero vector, resulting in the new vector  $\overline{\Lambda_{52}R^{\#}}$ .

the switching state changes to (4 2 1), which is a redundant state of the voltage space vector located at A25, which is the next vector to be switched, changing the state of phase A from three to four. The switching in PWM\_B will change the switching state to change from (4 2 1) to (4 3 1), changing the state of phase B from two to three. The switching state (4 3 1) represents the redundant state of the next vector to be switched in the sequence. The PWM\_C going high will change the switching state to (4 3 2) from (4 3 1), resulting in a change of state in phase C from one to two. Thus, the switching sequence is  $(3\ 2\ 1)\ (4\ 2\ 1)\ (4\ 3\ 2)\ during a sampling interval and (4\ 3\ 2)\ (4\ 3\ 1)\ (4\ 3\ 2)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\ 3\ 3)\ (4\$ 2 1)(3 2 1) for the subsequent interval. It may be noted that only one switching occurs as the inverter moves from one inverter state to another. Let us consider another reference space vectorA00R (Fig. 6). The switching voltage space vector located at A52 has two redundant states (2 0 3, 3 1 4). The switching vectors located at A17 and A53 have only one switching state each, which are(2 0 4) and (3 0 4), respectively. The switching vector located at A52 has the minimum value for the sum of magnitudes of the  $\alpha$  and  $\beta$  coordinates and is therefore selected as the virtual zero vector. Following the strategy explained earlier will result in the switching sequence for this sector as (2 0 3) (2 04 (304) (314) during a sampling interval and (314) (304) (204) (203) for the subsequent sampling interval, resulting in switching only in one phase as the inverter space vector moves from one vector to another. Therefore, in this paper, optimum switching sequence is achieved by adopting a strategy of selecting the switching state of the virtual zero vectors from the available redundancies. This simple strategy of choosing the switching states from the available redundant states achieves optimum switching in every sector and hence does not require lookup tables.

# E. Generating the Inverter Leg Switching Times in the Over Modulation Region

In the over modulation region, also the sector identification, switching vector determination, and determination of the virtual zero vector for the sector enclosing the reference space vector are done by utilizing the strategy explained earlier. It may be noted that, during over modulation, in the case of two-level inverter, zero vector will not be switched and, in the case of multilevel inverters, the virtual zero vector will not be switched so that the entire sampling period is shared by only two vectors. This principle is used to detect the over modulation region, and after mapping to the two-level inverter hexagon, T1 and T2time periods are modified so that Ts = T1 + T2 [12]. If an over modulation is detected (i.e., if T0 <0), the durations of the nonzero switching vectors are modified from T1 and T2 toT/1 and T/2, respectively

$$\begin{split} \mathbf{T}_{1}^{|} &= \frac{\mathbf{T}_{1}}{\mathbf{T}_{1} + \mathbf{T}_{2}} \mathbf{x} \mathbf{T}_{s} \quad (10) \\ \mathbf{T}_{2}^{|} &= \frac{\mathbf{T}_{2}}{\mathbf{T}_{1} + \mathbf{T}_{2}} \mathbf{x} \mathbf{T}_{s}. \quad (11) \end{split}$$

# IV. NEW SPACE VECTOR CONTROL APPROACH FOR FOUR SWITCH THREE PHASE INVERTER (FSTPI)

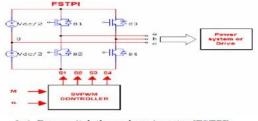

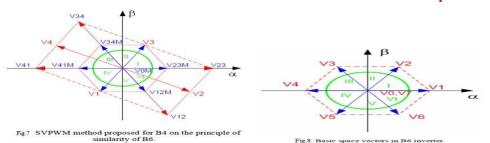

This paper is to present a space vector PWM algorithm for four switch three phase inverters (B4, FSTPI) based on the one for six switch three phase inverters (B6, SSTPI) (principle of similarity) where the  $\alpha\beta$  plan is divided into 6 sectors and the formation of the required reference voltage space vector is done in the same way as for B6 by using effective (mean) vectors. This facilitates the calculation for B4 and some studies on B6 can be applied forB4 as well through this proposed similarity B4 (Four Switch Three Phase Inverter), B6 (Six Switch Three Phase Inverter), The proposed SVPWM in this paper is based on the one for six switch three phase inverters (B6, SSTP) using principle of similarity where the  $\alpha\beta$  plan is divided into 6sectors and the formation of the required reference voltage space vector is done in the same way as for B6 by using the additional effective vectors. This facilitates the SVPWM calculation for B4 and some studies on B6 can be applied for B4 as well through this proposed approach.

# A. Proposed Method

Three phase variable speed drives for asynchronous motors have been used more and more, especially in energy saving drive applications for fans, pumps, air compressors... In many cases, the cost reduction is an important target for the drive. Hence, a reduced number of inverter switches is a promising solution. Several inverter schemes with reduced number of switches have been proposed. Among them the four switch three phase inverter (B4) (fig.1) was introduced with four IGBT switches instead of six (B6) in a conventional three phase inverters [1-8, 10]. In spite of the B4's drawbacks like a higher DC side capacitor voltage and unsymmetrical scheme exposed to the unbalanced

capacitor voltage, this inverter has the following advantages over B6 [2]: - The number of switches is reduced by a third; driving circuits are only two as only two branches are controlled. - In spite of the switch's higher withstandable voltage in B4 the cost is still lower thanks to the price ratio of B4 to B6 usually lower than 3/2. - B4's maximum common mode voltage is just2/3 of B6's.

fig, 4. Four switch three phase inverter (FSTPI)

According to the scheme in fig.1 the switching status is represented by binary variables S1 to S4, which are set to "1" when the switch is closed and "0" when open. In addition the switches in one inverter branch are controlled complementary (1 on, 1 off), therefore:

$$S1+S2 = 1, S3+S4 = 1$$

(1)

Phase to common point voltage depends on the turning off signal for the switch:

$$V_{a0} = (2S_1 - 1) \cdot \frac{V_{dc}}{2}; V_{b0} = (2S_3 - 1) \cdot \frac{V_{dc}}{2}; V_{c0} = 0;$$

(2)

Combinations of switching S1-S4 result in 4 general space vectors voltage vectors are gained from abc voltages by using Clark's transformation

$$\begin{bmatrix} V_{\alpha} \\ V_{\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_{a} \\ V_{b} \\ V_{c} \end{bmatrix}$$

(3)

Where Va, Vb, Vc : phase voltages on the load (Y connection), defined by

$$V_{a} = \frac{1}{3} (2V_{a0} - V_{b0}) ;$$

$$V_{b} = \frac{1}{3} (2V_{b0} - V_{a0});$$

$$V_{c} = -\frac{1}{3} (V_{a0} + V_{b0})$$

(4)

In order to form the required voltage space vector *ref V* we can use 3 or 4 vectors in one sampling interval Ts. The constant value 0 (zero) vectors can be formed by dividing t0 (duration of zero vector) among 2 opposite vectors.

| <b>S1</b> | \$3 | $\vec{V} = V_{\alpha} + j V_{\beta}$               |

|-----------|-----|----------------------------------------------------|

| 0         | 0   | $\vec{V}_1 = \frac{V_{dc}}{3}e^{-j\frac{2\pi}{3}}$ |

| 1         | 0   | $\vec{V}_2 = \frac{2V_{dx}}{3}e^{-j\frac{\pi}{6}}$ |

| 1         | 1   | $\vec{V}_{3} = \frac{V_{dc}}{2}e^{j\frac{\pi}{3}}$ |

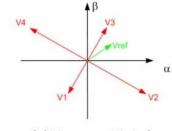

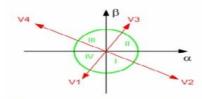

fig. 5 Voltage space vectors in the plan  $\alpha\beta$

Fig.6 Sectors used in conventional SVPWM methods for B4

SVPWM methods are based on the formation of the reference vector on the plan  $\alpha\beta$  which is divided into four sectors (sector I...IV). The active vectors and their duration in one sampling interval are selected and calculated on the basis of the required Vref location respective for these sectors (fig.3). SVPWM method proposed in this paper is based on the principle of similarity of the one for B6 inverters, where plan  $\alpha\beta$  is divided into 6 sectors and the formation of Vref is done similarly as for B6. This facilitates the calculation for B4 and some issues for B6 can be applied for B4 thanks to this proposed approach. To simulate 6 non-zero vectors in B6, in this proposed method, beside the two V1 and V3, we use the effective vectors V23M, V34M, V41M and V12M. These vectors are formed as follows:

$$\begin{split} \vec{V}_{23M} &= \frac{1}{2} \left( \vec{V}_2 + \vec{V}_3 \right) = \frac{V_{dc}}{3} e^{j0}; \vec{V}_{34M} = \frac{1}{2} \left( \vec{V}_3 + \vec{V}_4 \right) = \frac{V_{dc}}{3} e^{j\frac{2\pi}{3}}; \\ \vec{V}_{41M} &= \frac{1}{2} \left( \vec{V}_4 + \vec{V}_1 \right) = \frac{V_{dc}}{3} e^{j\pi}; \vec{V}_{12M} = \frac{1}{2} \left( \vec{V}_1 + \vec{V}_2 \right) = \frac{V_{dc}}{3} e^{-j\frac{\pi}{3}}; \end{split}$$

To simulate zero vectors of B6, we use the effective V0M

| SIMILARITY BETWEEN SPA              | CE VECTORS OF B4 AND B6     |

|-------------------------------------|-----------------------------|

| Base voltage space vectors<br>of B6 | Voltage space vectors of B4 |

| Vı                                  | V <sub>23M</sub>            |

| V <sub>2</sub>                      | $V_3$                       |

| V <sub>3</sub>                      | V <sub>34M</sub>            |

| V <sub>4</sub>                      | V <sub>41M</sub>            |

| V <sub>5</sub>                      | $V_1$                       |

| V <sub>6</sub>                      | V <sub>12M</sub>            |

| $V_0, V_7$                          | $V_{0M}$                    |

$\vec{V}_{0M} = \frac{1}{2} \left( \vec{V}_1 + \vec{V}_3 \right), \text{ or } \vec{V}_{0M} = \frac{1}{2} \left( \vec{V}_2 + \vec{V}_4 \right),$  (10)

B6 (Fig.5) is presented in Table 2. The base vectors in each sector used to form the required space vector Vref is presented in Table 3. Below we will describe the space vector modulation for B4 inverter based on the modulation for B6 with the principle of similarity

Fig.9 Pulse patterns for switching in the proposed method.

# V. CONCLUSION

The study of multilevel inverter gained more attention in recent years due to its inherent advantages of high Voltage-Ampere rating and good harmonic rejection capabilities. In this paper we discussed three different methods for implementation of PWM multilevel inverter. Two main PWM generating methods are Sine triangle PWM (SPWM) and Space Vector PWM (SVPWM) .Analyzing these methods we got SVPWM is better than SPWM because it has 1)better fundamental output voltage.2)better harmonic performance.3)easier implementation. This paper discussed a conventional method SSTPI (Six Switch Three Phase Inverter) but this method has very high computational

complexity because of the increased number of switches so in future work we can reduces the switches and that will reduces the complexity

#### REFERENCES

- [1] Anish Gopinath, Aneesh Mohamed A. S., and M. R. Baiju "Fractal based space vector PWM for multilevel inverters—A novel approach,", IEEE Trans. Ind. Electron., vol. 56, no. 4, pp.1230–1237, Apr. 2009

- [2] M. B. R. Corrêa, C. B. Jacobina, E. R. C. Silva and A. M. N. Lima, "A General PWM Strategy for Four-Switch three phase inverter," IEEE Trans. on Power Electronics, Vol. 21, No. 6, pp.1618-1627, Nov. 2006.

- [3] Aneesh Mohamed A.S., Anish Gopinath and M.R.Baiju, "A simple space vector PWM generation scheme for any general n-level inverter," IEEE Trans. Ind. Electron., vol. 56, no. 5, pp.1649-1656, May 2009.

- [4] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [5] J. Holtz, "Pulse width modulation—A survey," IEEE Trans. Ind.Electron., vol. 39, no. 5, pp. 410–420, Dec. 1992.

- [6] W. Yao, H. Hu, and Z. Lu, "Comparisons of space-vector modulation and carrier based modulation of multilevel inverter," IEEE Trans. Power Electron., vol. 23, no. 1, pp. 45–51, Jan. 2008.

- [7] K. Zhou and D. Wang, "Relationship between space-vector modulation and three-phase carrier-based *PWM: A comprehensive analysis,*" *IEEE Trans. Ind. Electron., vol. 49, no. 1, pp. 186–196, Feb. 2002.*